Renesas RX Cores

Renesas RX Cores are a number of cores used by Renesas' RX family of MCUs, that combine design elements of CISC and RISC cores.

J-Link and Flasher support

Both J-Link and Flasher support a growing number of Renesas RX devices.

Debugger Authentication

The on-chip debugging functions of RX devices include a protection through a 128 bit ID called ID Code.

The necessity of the debugger authentication depends on the device / device family.

Authentication process

J-Link / Flasher perform that authentication during the connect sequence.

Before performing the authentication itself, the RX core is identified, to decide which authentication mechanism is used.

- Check the authentication state

- Check if authentication is required

- Check if debugger is already authenticated

- Try to perform authentication [1] by sending three different ID Codes

- using all 0xFF

- using all 0x00

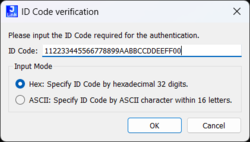

- using a custom ID Code, that can be defined multiple ways

- pre-defined using J-Link Command string SetRXIDCode

- pre-defined using J-Flash command-line argument -setrxidcode

- when using GUI application: entered when queried by dialog

- Check if debugger was successfully authenticated after each try.

- ↑

Depending on the specific core different registers and sequences are used to send the ID Code.

Debug Mode

In order to maintain the target connection under all circumstances, a debug mode is enabled on the target device.

That debug mode is enabled as part of the connect sequence and disabled on debug session close.

Doing so requires writing to the flash, which will be logged as a flash download during the connect sequence.