Gaisler NOEL-ARTYA7

Jump to navigation

Jump to search

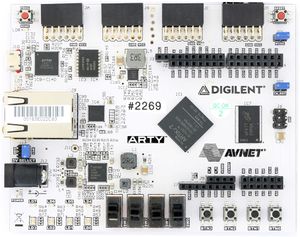

This article describes specifics for the Gaisler NOEL-ARTYA7. The Gaisler NOEL-ARTYA7 implements a Gaisler NOEL-V (64-bit RV64) core as a FPGA bitstream that runs on the Digilent ARTY-100T eval board.

Getting the bitstream running

Prerequisites

To program the bitstream:

- Gaisler NOEL-ARTYA7: gaisler.com

- Digilent ARTY-100T FPGA eval board (~200 EUR)

- Xilinx Vivado ML (free)

- Micro USB cable

Programming the bitstream

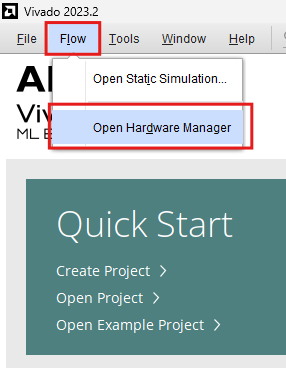

In this article, Vivado ML 2023.2 was used but the steps should be identical / very similar for later versions.

- Supply power to the ARTY-100T board via the power jack (7V, center positive)

- Connect the ARTY-100T board via micro USB cable to the computer

- Start Vivado ML

- Click Open Hardware Manager

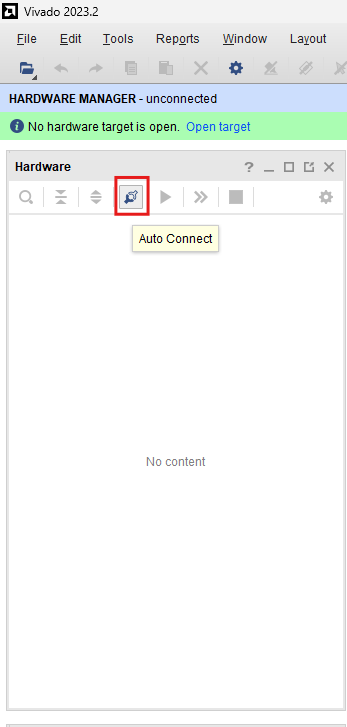

- Click Open Target -> Auto Connect

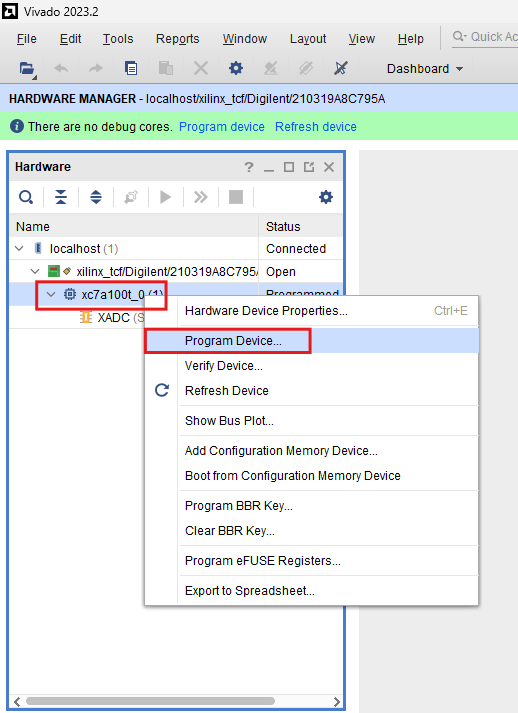

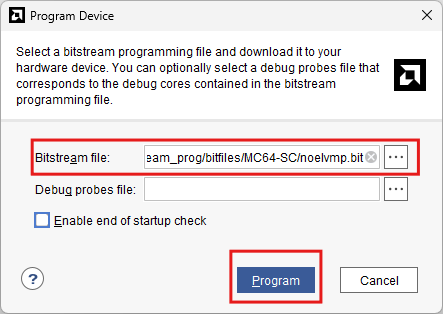

- Select FPGA -> Right-click -> Program Device

- Select the BIT file (bitstream) for the NOEL-V from the Gaisler dev kit package and press Program

The BIT file for the NOELV is located under: noel-arty-YYYYMM\bitfiles\MC64-SC\noelvmp.bit

- Wait until the DONE LED lights up.

- The noelvmp.bit file is loaded into FPGAs internal RAM and the configuration will be lost after powering down the board.

Troubleshooting

- Vivado ML Auto connect fails:

- The ARTY board sports a FTDI FT2232 chip for Flashing the FPGA. You will need to install the VCOM drivers.

- For Windows there is a setup exe which is recommended.

- Before installing make sure nothing is connected via USB.

- Now install the driver.

- Restart the PC

- If everything worked, once you connect USB port J10 from the board to your PC you should have a Composite device in your device manager.

- The Vivado ML setup may not successfully install on a guest OS inside a virtual machine. It is recommended to install and run Vivado ML on a native OS.

Verifying the debug connection

Prerequisites

- J-Link BASE or higher: Model overview

- J-Link software package

Connecting to the device

- Connect the J-Link to this pins:

| J-Link Pin | Connector | Pin | Name |

|---|---|---|---|

| VTref | PMOD-JA | 6 | VCC |

| GND | PMOD-JA | 5 | GND |

| TDI | PMOD-JA | 7 | TDI |

| TMS/SWDIO | PMOD-JA | 8 | TMS |

| TCK/SWCLK | PMOD-JA | 3 | TCK |

| TDO/SWO | PMOD-JA | 1 | TDO |

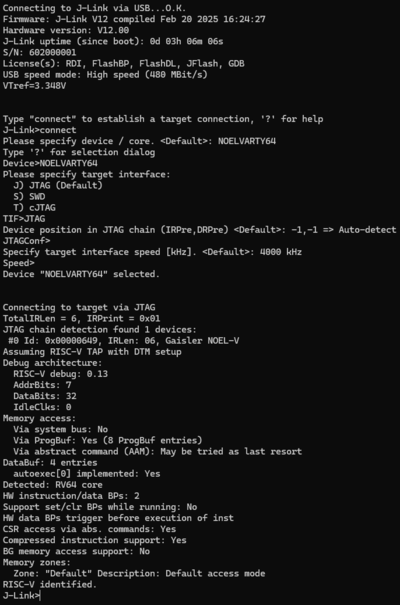

- Verify the Connection with e.g. J-Link Commander with device selection NOELVARTY64 and TIF == JTAG. The output should look as follows:

Example Project

The following example project was created with the SEGGER Embedded Studio project wizard and runs out-of-the-box on the Gaisler NOEL-ARTYA7.

It is a simple Hello World sample linked into the internal flash.

SETUP

- Embedded Studio: V8.22a

- Hardware: Gaisler NOEL-ARTYA7

- Link: File:Gaisler NOEL-V RV64 TestProject ES V822a.zip