Espressif ESP32-C5-DevKitC-1

Jump to navigation

Jump to search

This article describes specifics for the Espressif ESP32-C5-DevKitC-1 evaluation board.

File:ESP32-C5-DevKitC-1 board.png

Preparing for J-Link

- Enable external JTAG interface using the following link ESP32 external JTAG interface

- Connect the J-Link to this pins:

| J-Link Pin | Connector | Pin | Name |

|---|---|---|---|

| VTref | J1 | 1 | 3V3 |

| GND | J1 | 15 | GND |

| TDI | J1 | 4 | MTDI |

| TMS/SWDIO | J1 | 3 | MTMS |

| TCK/SWCLK | J3 | 8 | MTCK |

| TDO/SWO | J3 | 9 | MTDO |

| RESET | J1 | 2 | RST |

- Power the board via USB Type-C to UART Port

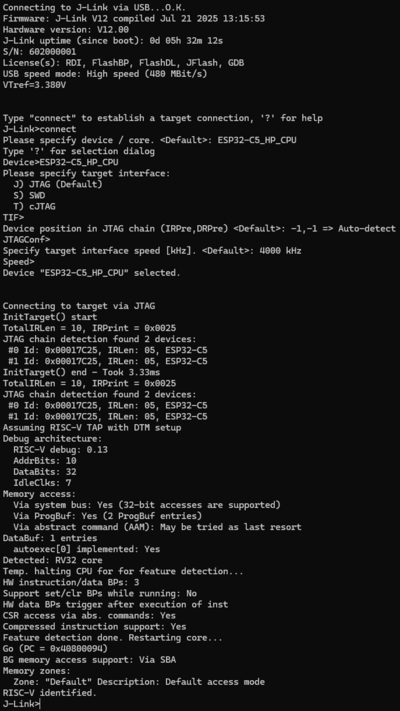

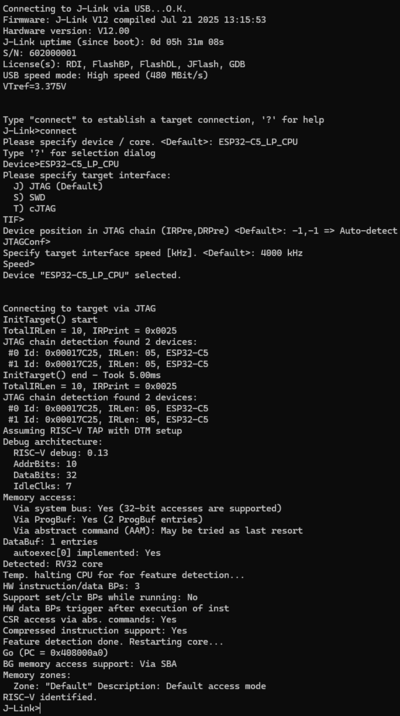

- Verify the Connection with e.g. J-Link Commander. The output should look as follows:

- HP core:

- LP core:

Example Project

The following example project was created with the SEGGER Embedded Studio project wizard and runs out-of-the-box on the Espressif ESP32-C5-DevKitC-1.

It is a simple Hello World sample linked into the internal SRAM.

SETUP

- Embedded Studio: V8.24

- Hardware: Espressif ESP32-C5-DevKitC-1

- Link: File:Espressif ESP32-C5-DevKitC-1 TestProject ES V824.zip