Infineon XMC7000

The Infineon XMC7000 are Cortex-M based microcontrollers. They consist of one Cortex-M0 core and up to two Cortex-M7 cores.

Flash Banks

Internal Flash

| Flash Bank | Base address | Size | J-Link Support |

|---|---|---|---|

| Code flash large area | 0x10000000 | 8 MB | |

| Code flash small area | 0x107F0000 | 192 KB | |

| Work flash large area | 0x14000000 | 192 KB | |

| Work flash small area | 0x14030000 | 64 KB |

Watchdog Handling

- The device has a watchdog WDT.

- If the watchdog is enabled, it is turned off during flash programming and turned back on afterwards.

Device Specific Handling

Reset

- The devices uses normal Cortex-M reset for Cortex-M0 core, no special handling necessary, like described here.

- The devices does not perform a reset for Cortex-M7 cores.

Limitations

Device support has been implemented and is maintained / supported by Infineon. SEGGER ships the provided files as part of the software package but in case of any problems / question rise up, Infineon is the right contact.

Evaluation Boards

- Infineon XMC7200 Evaluation Kit: https://wiki.segger.com/Infineon_XMC7200_Evaluation_Kit

Example Application

- Infineon XMC7200 Evaluation Kit: https://wiki.segger.com/Infineon_XMC7200_Evaluation_Kit#Example_Project

Tracing on Infineon XMC7200

This section describes how to get started with trace on the Infineon XMC7200 MCUs. This section assumes that there is already a basic knowledge about trace in general (what is trace, what different implementations of trace are there, etc.). If this is not the case, we recommend to read Trace chapter in the J-Link User Manual (UM08001).

Some of the examples are shipped with a compiled .JLinkScriptfile (extension .pex), should you need the original source, please get in touch with SEGGER directly via our support system: https://www.segger.com/ticket/.

To create your own .JLinkScriptfile you can use the following guide as reference: How_to_configure_JLinkScript_files_to_enable_tracingMinimum requirements

In order to use trace on the Infineon XMC7200 MCU devices, the following minimum requirements have to be met:

- J-Link software version V8.10b or later

- Ozone V3.38 or later (if streaming trace and / or the sample project from below shall be used)

- J-Trace PRO for Cortex-M HW version V3.0 or later for streaming trace

- J-Link Plus V12 or later for TMC/ETB trace

To rebuild the project our IDE Embedded Studio can be used. The recommended version to rebuild the projects is V8.16. But the examples are all prebuild and work out-of-the box with Ozone, so rebuilding is not necessary.

CM7

The project below has been tested with the minimum requirements mentioned above and a KIT_XMC72_EVK.

- Example project: Infineon_XMC7200_M7_TraceExample.zip

Streaming trace

Open the *_TracePins.jdebug project contained in the example project in Ozone.

Trace buffer (TMC/ETB)

Open the *_TraceBuffer.jdebug project contained in the example project in Ozone.

CM0+

The project below has been tested with the minimum requirements mentioned above and a KIT_XMC72_EVK.

- Example project: Infineon_XMC7200_M0_TraceExample.zip

Trace buffer (TMC/ETB)

Open the *_TraceBuffer.jdebug project contained in the example project in Ozone.

Tested Hardware

Specifics/Limitations

The KIT_XMC72_EVK needs some modifications for all 4 trace data pins to work. For more information about this see the board specific user manual.

The PinTrace initialisation is done in the DLL so the trace examples do not use an pex file. If your hardware uses a different trace pin layout, please get in touch with SEGGER directly via our support system: https://www.segger.com/ticket

Reference trace signal quality

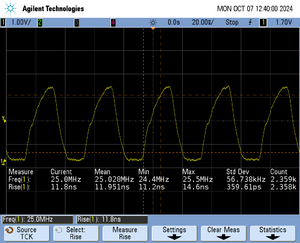

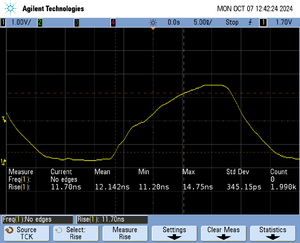

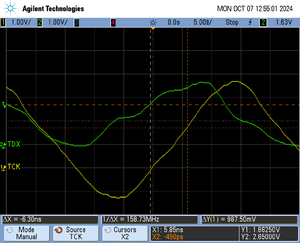

The following pictures show oscilloscope measurements of trace signals output by the "Tested Hardware" using the example project. All measurements have been performed using a Agilent InfiniiVision DSO7034B 350 MHz 2GSa/s oscilloscope and 1156A 1.5 GHz Active Probes. If your trace signals look similar on your trace hardware, chances are good that tracing will work out-of-the-box using the example project. More information about correct trace timing can be found at the following website.

Trace clock signal quality

The trace clock signal quality shows multiple trace clock cycles on the tested hardware as reference.

Rise time

The rise time of a signal shows the time needed for a signal to rise from logical 0 to logical 1. For this the values at 10% and 90% of the expected voltage level get used as markers. The following picture shows such a measurement for the trace clock signal.

Setup time

The setup time shows the relative setup time between a trace data signal and trace clock. The measurement markers are set at 50% of the expected voltage level respectively. The following picture shows such a measurement for the trace data signal 0 relative to the trace clock signal.