Syntacore SCR1 SDK Arty: Difference between revisions

No edit summary |

(Removed H1 (only one allowed per page and that is defined by the title already!)) |

||

| Line 4: | Line 4: | ||

This article describes specifics for the Syntacore SCR1 Arty SDK. | This article describes specifics for the Syntacore SCR1 Arty SDK. | ||

= J-Link support = | == J-Link support == | ||

= Hardware requirements = | == Hardware requirements == | ||

Please note that a current J-Link model is needed for RISC-V support: [[Software and Hardware Features Overview | Overview]] | Please note that a current J-Link model is needed for RISC-V support: [[Software and Hardware Features Overview | Overview]] | ||

= Software requirements = | == Software requirements == | ||

J-Link software [https://www.segger.com/downloads/jlink/#J-LinkSoftwareAndDocumentationPack V6.44] or later is required to support the Syntacore SCR1. Older versions will not work. | J-Link software [https://www.segger.com/downloads/jlink/#J-LinkSoftwareAndDocumentationPack V6.44] or later is required to support the Syntacore SCR1. Older versions will not work. | ||

= Example projects = | == Example projects == | ||

Please refer to the [[Syntacore SCR1]] article to see what sample projects are available. | Please refer to the [[Syntacore SCR1]] article to see what sample projects are available. | ||

= Preparing for J-Link = | == Preparing for J-Link == | ||

Initially, the Arty board does not run any Syntacore SCR1 core, so the FPGA on it needs to be configured first. For instructions how to do this, please refer to | Initially, the Arty board does not run any Syntacore SCR1 core, so the FPGA on it needs to be configured first. For instructions how to do this, please refer to | ||

Latest revision as of 18:03, 6 December 2024

This article describes specifics for the Syntacore SCR1 Arty SDK.

J-Link support

Hardware requirements

Please note that a current J-Link model is needed for RISC-V support: Overview

Software requirements

J-Link software V6.44 or later is required to support the Syntacore SCR1. Older versions will not work.

Example projects

Please refer to the Syntacore SCR1 article to see what sample projects are available.

Preparing for J-Link

Initially, the Arty board does not run any Syntacore SCR1 core, so the FPGA on it needs to be configured first. For instructions how to do this, please refer to

GitHub Syntacore SCR1 ARTY image

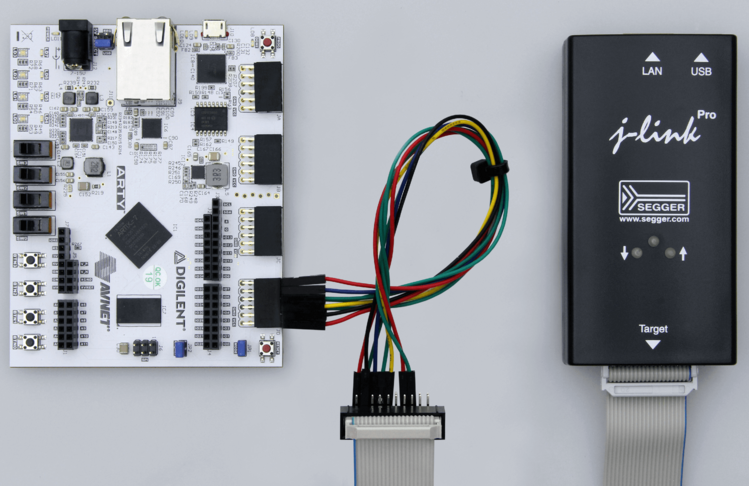

The Syntacore SCR1 Arty SDK does not come with a standard debug connector but populates the debug JTAG signals on a custom connector. Therefore, it needs to be manually wired in case J-Link shall be connected to it.

In the following, it is described how the pins of connector JD on the ARTY board needs to be wired to J-Link. All pins of the J-Link side refer to the standard 0.1" 20-pin connector of J-Link.

| Pin JD (ARTY) | Pin J-Link | Description |

|---|---|---|

| 3 | 3 | nTRST |

| 4 | 9 | TCK |

| 7 | 13 | TDO |

| 8 | 5 | TDI |

| 9 | 15 | nRESET |

| 10 | 7 | TMS |

| 11 | 4 | GND |

| 12 | 1 | VCC/VTref |

Note: The pins on the JD connector are numbered as follows:

| 6 | 5 | 4 | 3 | 2 | 1 |

| 12 | 11 | 10 | 9 | 8 | 7 |